Verkor tocmai a prezentat Design Conductor, un agent AI care a construit autonom un CPU RISC-V capabil să ruleze Linux. Sistemul a generat în 12 ore mai multe variante de microarhitectură pentru procesorul VerCore, pornind de la un document de cerințe de doar 219 cuvinte.

Design Conductor este un agent autonom pentru proiectare de semiconductori, creat pentru a duce un chip de la concept la GDSII, adică fișierul CAD de layout folosit înainte de producția fizică. În cazul VerCore, echipa Verkor susține că agentul a produs un design verificat, tape-out ready, cu frecvență de 1,48 GHz și scor CoreMark de 3261.

Design Conductor a construit un CPU RISC-V complet

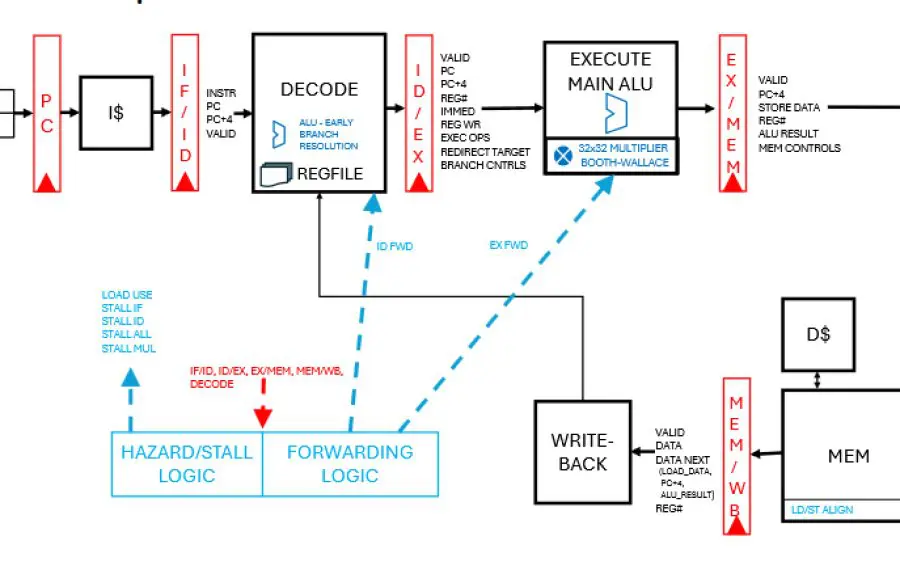

Procesorul rezultat, numit VerCore, implementează RV32I și extensia ZMMUL, cu o arhitectură simplă de tip 5-stage pipeline, in-order și single-issue. Specificația inițială cerea interfețe separate pentru instruction cache și data cache, datapath de 32 de biți, suport pentru reset activ pe low și o țintă de frecvență de 1,6 GHz.

VerCore nu suportă instrucțiuni comprimate, iar registrul intern este implementat cu flip flops, astfel încât citirile pot avea loc oricând în ciclu, iar scrierile se fac la următorul front crescător de frecvență. Agentul a trebuit să se ocupe atât de RTL, adică descrierea logică a circuitului, cât și de designul fizic prin OpenROAD flow scripts și platforma ASAP7.

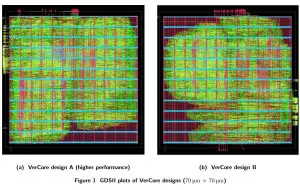

Rezultatul final raportat este un CPU cu suprafață de 2809 µm², fără cache, realizat pe tehnologie ASAP7. La nivel de context istoric, autorii compară performanța cu un Intel Celeron SU2300 din 2011, care rula la 1,2 GHz, comparație utilă mai ales pentru a arăta ordinul de mărime, nu pentru a sugera o comparație reală cu procesoare moderne.

De la cerințe la GDSII, fără intervenție umană directă

Verkor consideră că acesta este primul caz în care un agent autonom a construit un CPU complet și funcțional de la specificație până la GDSII. GDSII este formatul folosit pentru reprezentarea finală a layoutului unui circuit integrat, deci trecerea până în acest punct este mult mai relevantă decât simpla generare de cod Verilog.

Design Conductor a pornit prin generarea unei propuneri de arhitectură, apoi a făcut review asupra propriului design, a implementat modulele RTL și a construit testbenchuri pentru fiecare componentă. Agentul a folosit Spike, simulatorul oficial RISC-V ISA, pentru a verifica dacă starea arhitecturală și tranzacțiile de memorie ale procesorului corespund cu rezultatele așteptate.

Procesul descris nu este „vibe chip design”, formulare pe care autorii o resping explicit, ci o buclă de implementare, testare și corectare bazată pe simulări și rapoarte. Într-un exemplu, agentul a analizat fișiere VCD, le-a convertit în CSV și a urmărit diferențe între scrierile reale în registre și traseul așteptat, identificând o problemă de pipeline flush după o instrucțiune JAL.

VerCore folosește optimizări găsite de agent

În etapa de închidere PPA, adică power, performance and area, Design Conductor a analizat rapoarte de timing și a modificat RTL-ul pentru a îmbunătăți designul. Agentul a implementat early forwarding în etapa ID și un multiplicator Booth-Wallace rapid, cu 4 stadii, care separat poate atinge 2,57 GHz.

Diagrama pipeline-ului final arată un design cu rezolvare timpurie a branchurilor, forwarding logic, hazard/stall logic, Booth-Wallace multiplier și etapele clasice IF, ID, EX, MEM și WB. Autorii spun că agentul a testat mai multe variante, inclusiv unele cu penalizare de branch de 2 cicluri și altele cu penalizare de 1 ciclu, înainte de a alege varianta cu performanța mai bună.

Această parte este importantă deoarece arată că agentul nu a completat doar un șablon de CPU. Design Conductor a explorat mai multe opțiuni arhitecturale, a rulat backend-ul până la GDSII pentru fiecare variantă și a decis pe baza constrângerilor de timing.

Limitele AI rămân vizibile

Documentul publicat nu prezintă Design Conductor ca înlocuitor complet pentru arhitecții umani. Autorii notează că modelele AI încă au dificultăți în raționamentul arhitectural și pot face alegeri suboptime care consumă multe tokens înainte să fie corectate prin feedback din tool-uri.

Un exemplu menționat este tendința modelului de a trata uneori Verilog ca pe cod secvențial, deși limbajul descrie logică hardware cu comportament bazat pe evenimente. Într-un caz, agentul a presupus greșit că reducerea numărului de linii dependente ar scurta automat critical path-ul în chip, o confuzie tipică atunci când experiența de software este aplicată prea direct peste hardware.

Concluzia autorilor este că sisteme precum Design Conductor pot reduce radical timpul de explorare și implementare, dar au nevoie în continuare de arhitecți experimentați care să formuleze cerințe măsurabile și să ghideze obiectivele. Verkor estimează că echipele viitoare ar putea explora mai multe designuri până la GDSII și ar putea reduce ciclurile pentru chipuri complexe de la 18-36 luni la 3-6 luni.

Dacă aceste rezultate se confirmă în proiecte comerciale, schimbarea reală nu va fi că AI-ul „inventează” procesoare peste noapte. Va fi faptul că munca lentă, repetitivă și costisitoare din RTL, verificare, backend și optimizare ar putea deveni un proces iterativ mult mai rapid, în care inginerii decid mai mult direcția, iar agentul suportă partea de execuție.